以路由器(router)为DUT,逐步搭建其testbench的过程

2022-12-10

SystemVerilog课程笔记(十一)

SystemVerilog课程笔记(十一)

SystemVerilog课程笔记(十)

SystemVerilog课程笔记(十)

SystemVerilog课程笔记(九)

SystemVerilog课程笔记(九)

使用PLI接口实现故障注入

使用PLI接口实现故障注入

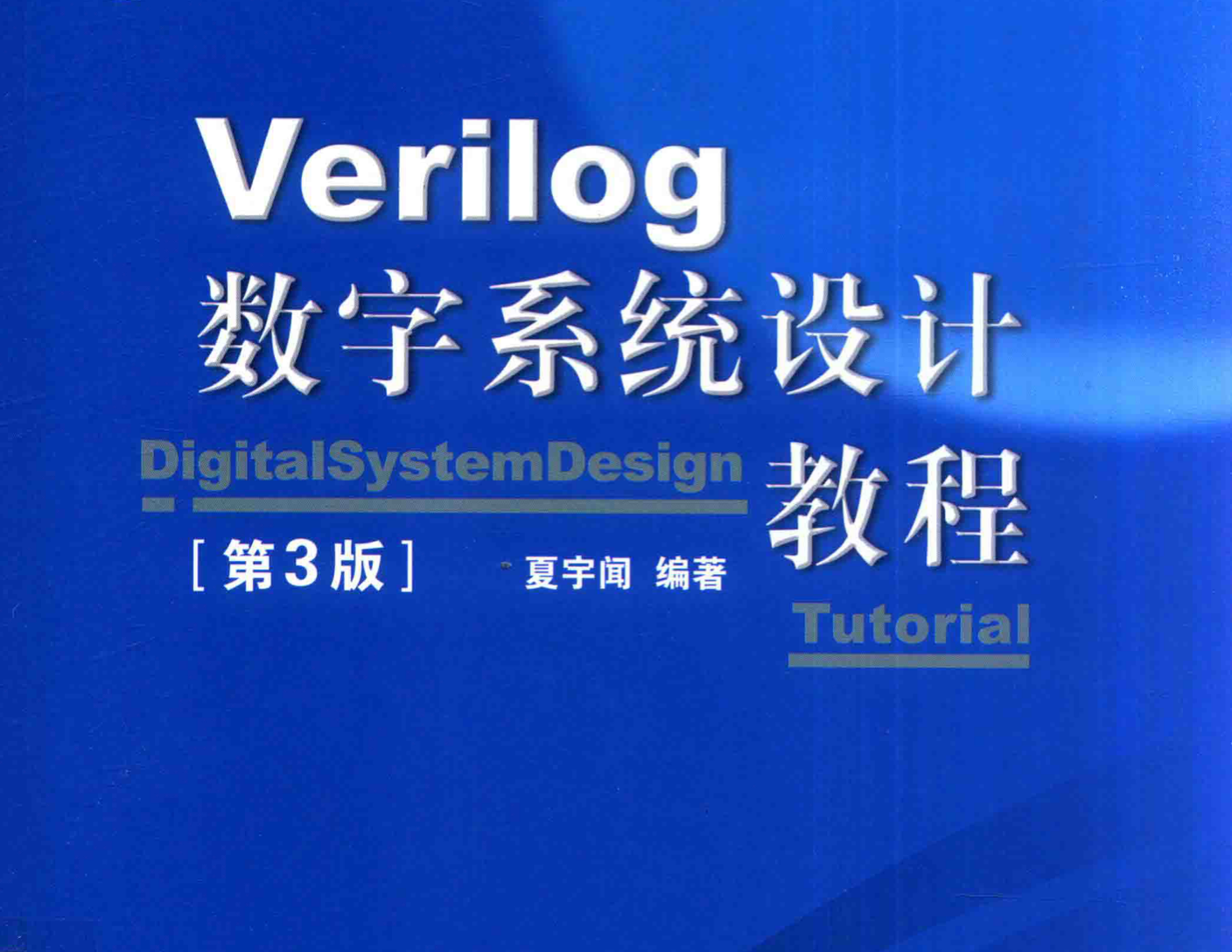

Verilog数字系统设计第(三)章总结

Verilog数字系统设计第(三)章总结

SystemVerilog学习笔记(十)

SystemVerilog学习笔记(十)

SystemVerilog学习笔记(九)

SystemVerilog学习笔记(九)

SystemVerilog实验(一)

SystemVerilog实验(一)

SystemVerilog课程笔记(八)

SystemVerilog课程笔记(八)

SystemVerilog学习笔记(八)

SystemVerilog学习笔记(八)