名词解释

OBC——星载计算机(On-Board Computer,OBC)

SIP——系统级封装

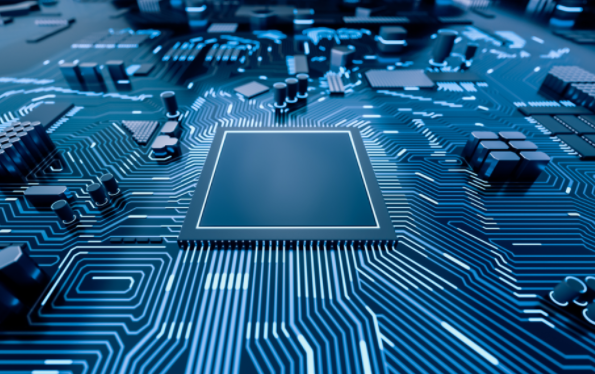

空间环境中的辐射效应

总剂量效应

单粒子效应

抗辐照性能的评估方法

空间环境实验

空间环境实验以及地面模拟等效实验都有几个很明显的缺点:首先是需要搭建实验评估环境,致使试验成本升高;其次是需要对待评估的模块进行流片试产,如果辐照评估出现问题就会重新调试生产,导致设计周期变长;最后是在实验中观察到单粒子效应后,对系统的错误定位也是目前的技术难点。

地面模拟等效实验

随着SiP 封装技术在航天星载计算机设计领域的普及,需要对SiP 封装的芯片进行 辐射效应评估,由于地面实验的加速器粒子能量不够,导致在进行地面辐照试验时难以穿透SiP 封装腔体,所以不能有效的对系统进行评估。

计算机数值模拟仿真

而使用计算机仿真技术对星载计算机系统进行抗辐照性能评估,使得设计人员能在设计初期对系统可靠性有准确把握。使用计算机仿真软件可以对空间粒子在器件上的作用机理进行模拟仿真,具有效率高、成本低和效果好等诸多优点。

单粒子效应仿真方法

器件级仿真

器件级单粒子效应仿真是通过 TCAD 仿真工具对器件或者小型电路进行建模,通过求解三大方程得到精确的器件模型。最后来模拟空间环境对器件模型产生的辐照效应,以实现对单粒子效应进行分析,是目前业内单粒子效应机理研究方向的主要仿真方法。

电路级仿真

电路级单粒子效应仿真忽略了器件底层的物理细节,更加偏重晶体管层面的仿真,通过用SPICE 工具支持的语法描述单粒子脉冲,实现对电路的单粒子效应故障注入。是研究模拟电路以及小规模数字电路单粒子效应的主流仿真手段。

逻辑门级仿真

逻辑门级仿真主要是通过预设网表中每个逻辑门的单位时间故障(Failure in Time,FIT),然后分析Verilog 门级网表结构,从而得到整个门级网表的FIT 和软错误率,这种仿真方法有着计算速度快,支持电路规模大的特点。

RTL 级仿真

RTL 级故障注入仿真对电路系统的 RTL 级模型进行仿真,由于仿真方法的模型层次较高因此仿真速度也最快。

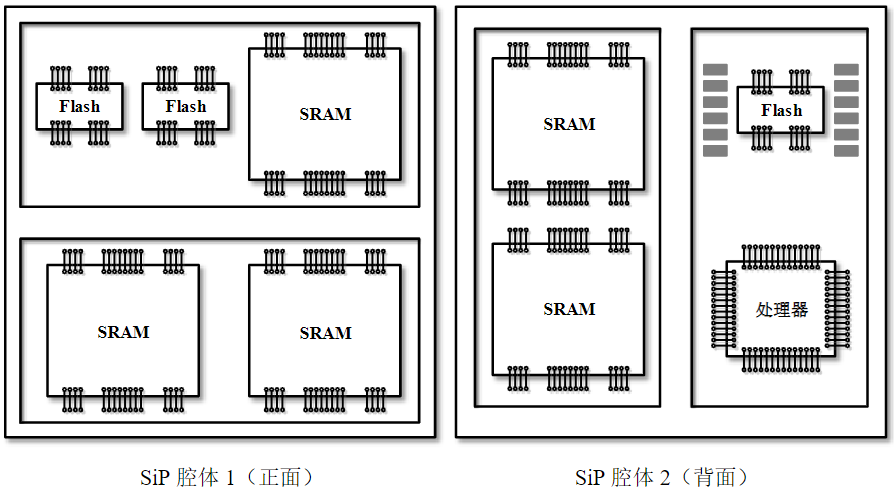

星载计算机系统

通过SiP 封装技术,将系统各模块封装在两个腔体中,其中腔体1 中包括了3 片SRAM 芯片以及两片Flash 芯片,而腔体2 中包括了2 片SRAM 芯片、一片Flash 芯片以及处理器芯片。系统使用倒装技术,片间用金键合丝以及TSV 等技术实现系统互连。

- 处理器模块是基于SPARC V8 指令集架构的开源LEON处理器进行开发设计,该模块在系统中负责对外设的控制与通信,程序的读取与执行,是系统的核心。

- Flash 与部分SRAM 模块负责程序指令的存储,

- 其余SRAM 模块负责保存系统的运行数据。

当系统上电后,处理器先读取保存在Flash 中的boot 初始化程序,对系统寄存器等模块初始化之后,将后续执行的程序,从Flash 转存至指令SRAM中,随后地址跳转到指令SRAM 进行程序的取指、译码、执行、访存、回写等操作。

SRAM的加固 ^a9ac5d

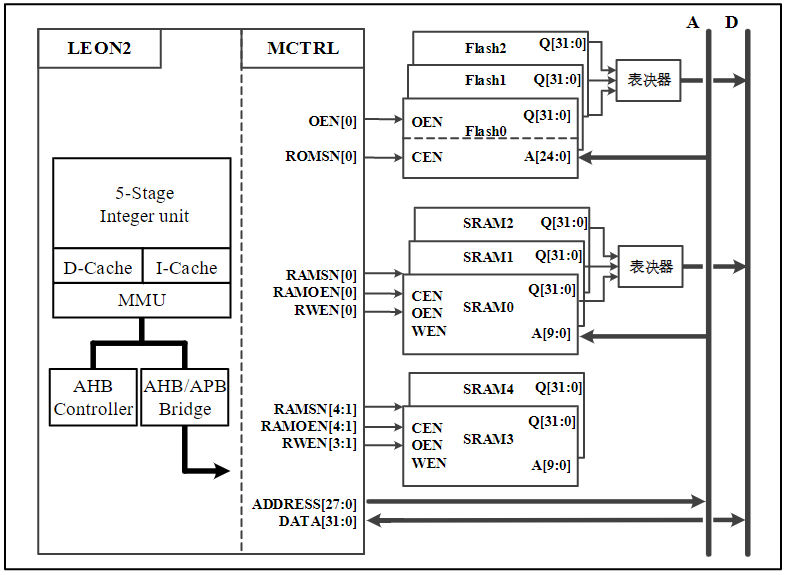

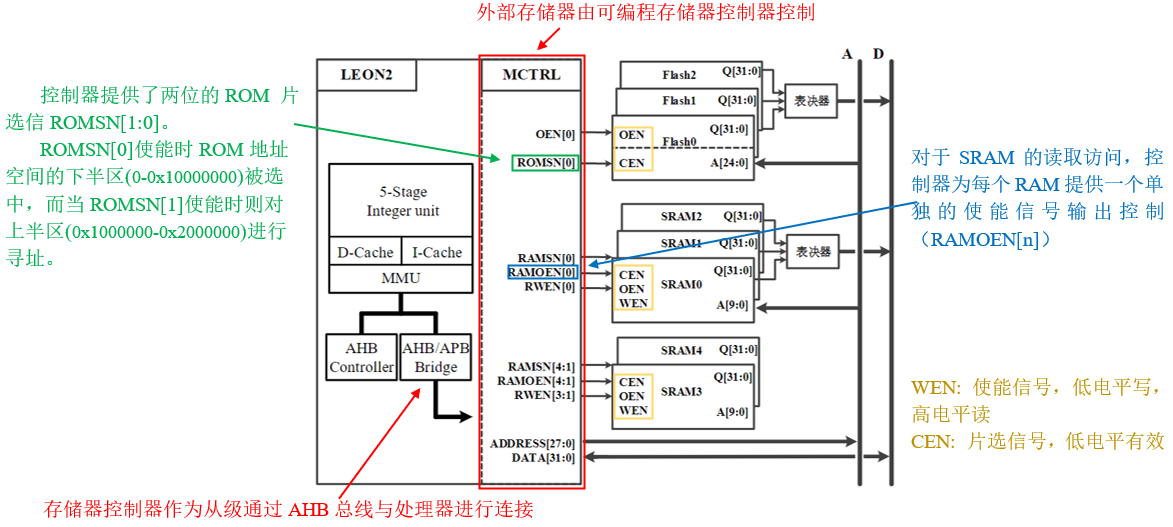

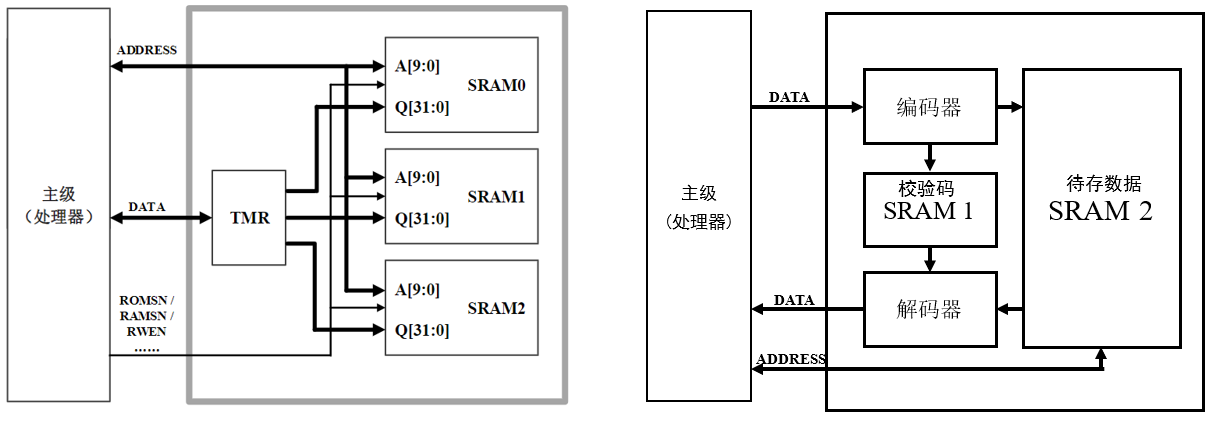

对存有初始化程序的 Flash,以及存有指令的 SRAM 进行了模块级的三模冗余(Triple Modular Redundancy,TMR)加固设计。

加固设计后的目标系统结构就变为下图

在为星载计算机系统存入程序时,对三块 Flash 和指令 SRAM 都存储相同的程序,这样在收到外部读取请求信号时,存储器的输出端口中所有数据位都先会通过三输入表决器后再输出到数据总线,从而提高了系统在辐照环境下的工作稳定性。

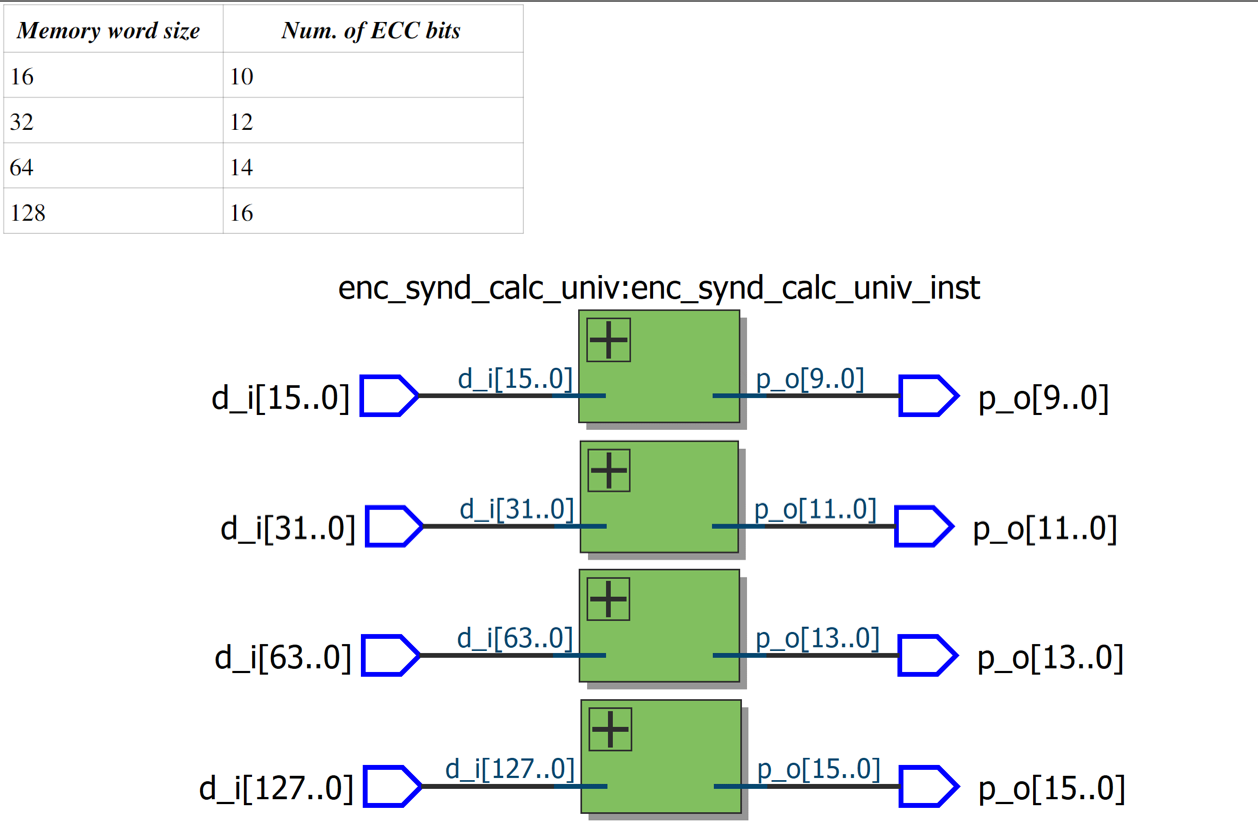

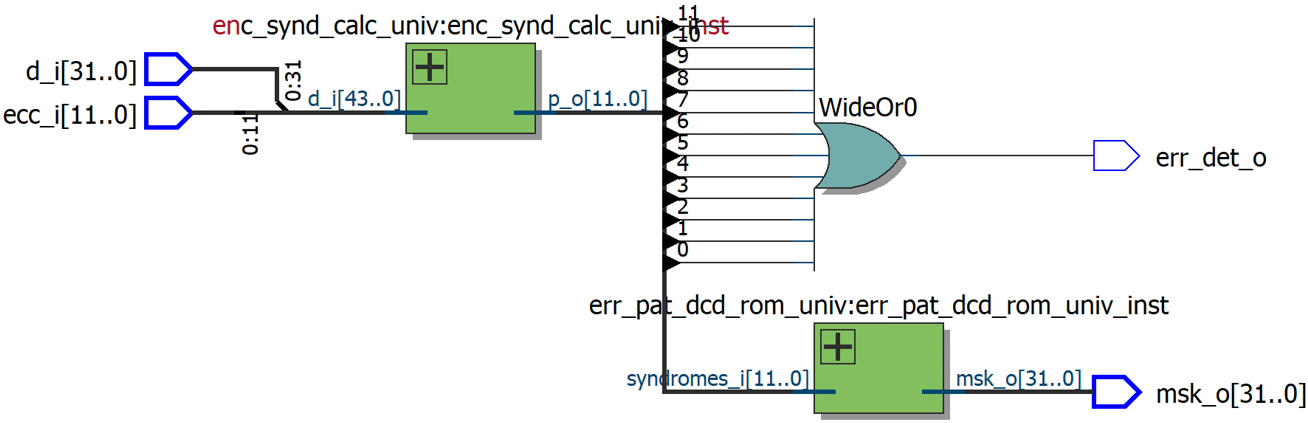

采用ECC算法进行SRAM加固模块如下

^df961a

^df961a

星载计算机系统模型的搭建

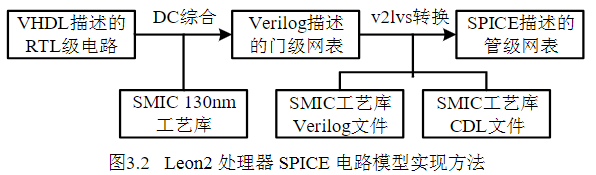

leon2处理器建模(管级网表的提取)

想要对OBC-SiP 系统进行单粒子效应仿真,首先就必须得到OBC-SiP 的系统模型。

Leon2 开源代码由可综合的超高速集成电路硬件描述语言(VHDL)代码构成,为了建立 Leon2 处理器的 SPICE 电路模型并进行单粒子效应仿真,需要将 Leon2 处理器寄存器传输 级(RTL)的 VHDL 代码转换为 SPICE 描述的晶体管级网表,

需要如下两个步骤:

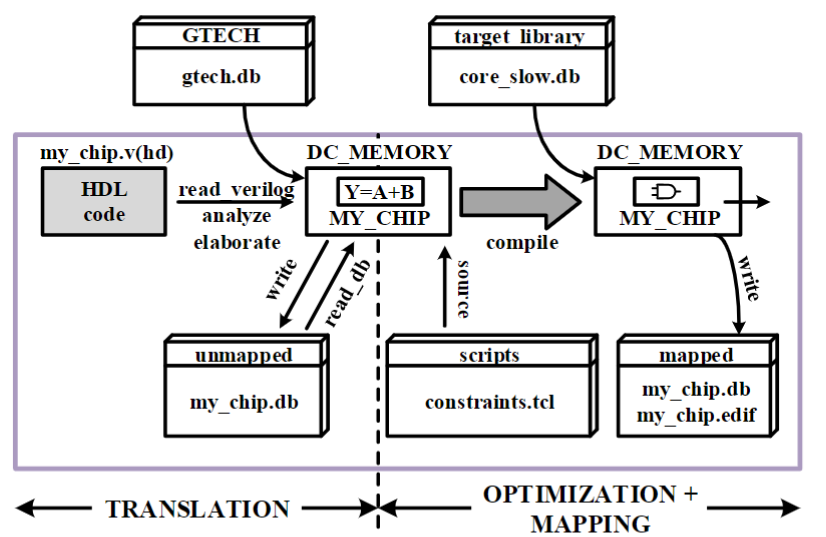

DC综合

- 转换

综合工具首先会将 Leon2 处理器的 VHDL 的描述转换成一个与工艺独立的 RTL 级网表(网表中 RTL 模块通过连线互联)。 - 映射

然后根据具体指定的工艺库,将 RTL 级网表映射到工艺库上,成为一个门级网表。 - 优化

最后再根据设计者施加的诸如延时、面积方面的约束条件,对门级网表进行优化。[!info]+ DC综合

Synopsys 公司的DC(Design Compiler)是目前业内使用最广泛的电路综合工具,可以很方便地将硬件描述语言的可综合代码设计转换到基于标准单元库的门级网表。

DC 主要包括转换(translation)、映射(mapping)及优化(optimization)三个步骤。

综合工具首先将电路设计代码设计读入内存,用“gtech.db”库中的基本单元将设计转换为基本电路,然后根据综合人员给定的约束设置,对电路性能、面积等参数进行计算并优化,然后将优化之后的电路映射到用户设定的工艺库上

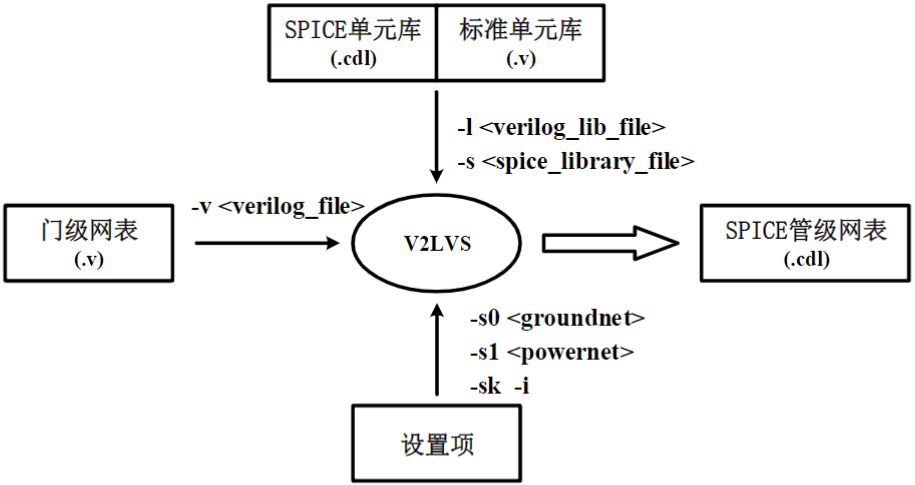

管级网表转换

Mentor 公司提供的 Calibre工具在数字 IC 后端设计中具有广泛的应用。其中 v2lvs命令可以将 DC 综合生成的门级网表转换为 SPICE 管级网表,为后续的处理器故障注入仿真提供基础文件。

[!info]+ 管级网表转换

Mentor Graphics 公司的Calibre 工具在IC 后端设计中必不可少,其中Calibre 中的v2lvs 命令能够很方便的将Verilog 的门级网表转换成我们所需要的SPICE 管级网表

存储器模块建模

Flash模块建模

Flash 主要器件结构是浮栅晶体管等特殊器件,由于其工艺的特殊性,无法建立该模块的SPICE 晶体管级模型,因此只对Flash 模块进行行为级建模。

SRAM 模块建模

SRAM 模块内部由多个子模块组成,可以大致分为:存储单元电路模块、逻辑接口电路模块、行译码电路模块、列译码器和灵敏放大器电路模块几个部分。存储器设计流程与上文中LEON2 处理器设计流程不同,并且灵敏放大器电路等模块和存储单元等模块使用工艺不同,无法按照“DC 综合-管级网表转换”这样的流程来进行建模。采用 Memory Compiler 工具,直接生成其行为级模型和 SPICE 管级模型

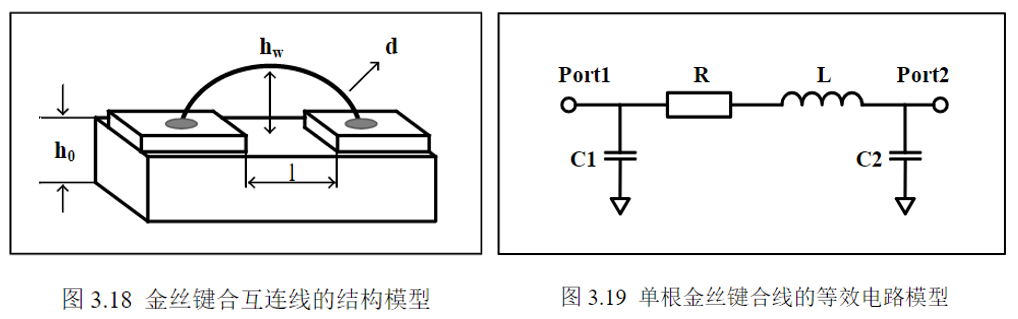

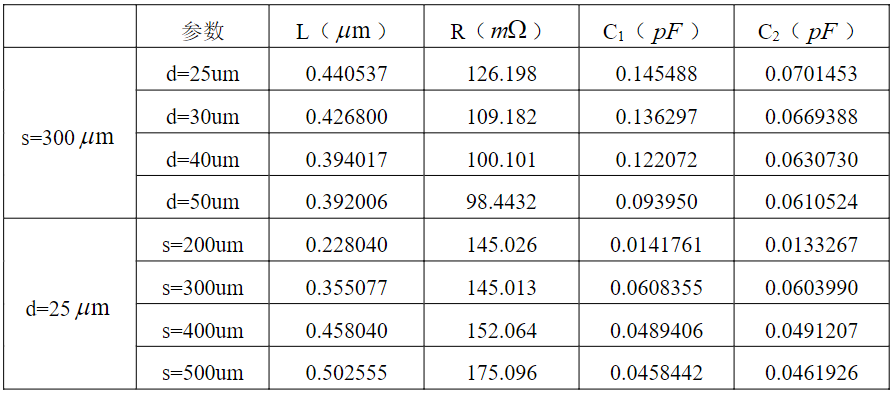

SiP 互连建模

单根金丝可以用图示的简化模型进行电路等效

在对系统各模块进行连接时,依据项目组提供资料,为键合金丝的等效模型选择合适的寄生参数,在SPICE 网表中将系统各模块的端口进行连接。

星载计算机系统模型构建( Leon2 处理器+外部电路)

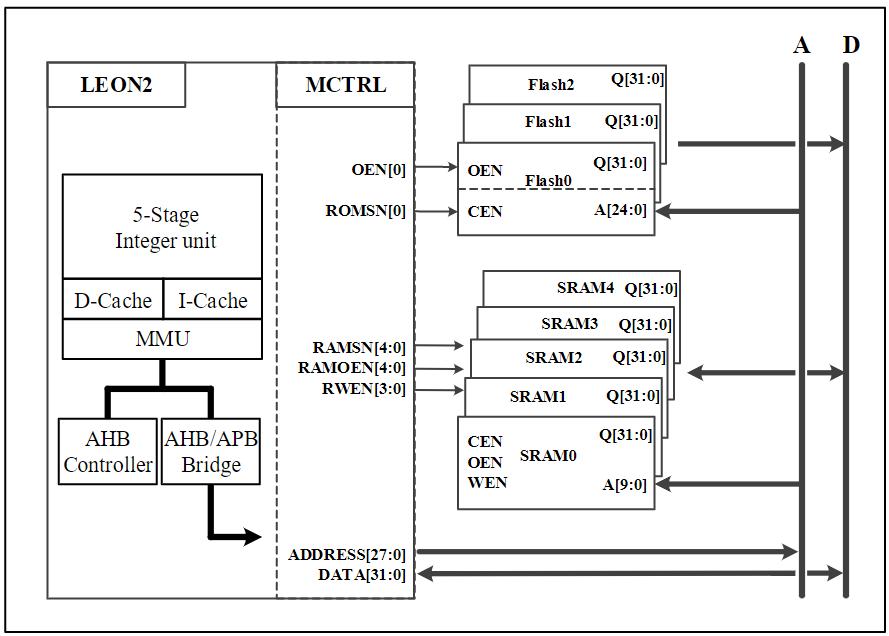

完成了 OBC-SiP 系统中各模块电路的建模工作之后,就可以对整个目标系统进行模型搭建。依据LEON2 处理器中的可编程存储器控制器设计要求,以及各存储模块的读写时序,通过连线将各模块进行连接,最终得到整个OBC-SiP 目标系统模型。

根据获得的 Leon2 处理器 SPICE 管级网表模型,对其进行外部电路扩展,构成一个小型的星载计算机系统模型,在该模型中存在以下几个模块:①Leon2 处理器核;②指令 SRAM 模块;③数据 SRAM 模块;④初始化指令 SRAM 模块。

单粒子效应故障注入技术

对于故障注入技术,按照注入的电路层次不同,可以分为硬件故障注入,软件故障注入,RTL 级故障注入与 SPICE 网表故障注入等。

软件层次故障注入技术

软件故障注入技术是在软件层次来实现处理器的故障注入方法,在处理器程序编译或者运行时动态的修改执行程序,或者人为设置寄存器值来改变处理器的运行状态。

优点

- 成本低,故障注入位置灵活可控,具有相当高的自由性。

- 可通过脚本或者程序可以实现批量的故障注入操作,完成故障注入的全自动化设置。

缺点

- 只能对计算机体系结构中可配置的寄存器进行故障注入设置,无法对不可配置部分进行故障注入,具有局限性,无法实现对整体芯片的抗辐射可靠性评估。

- 软件层次注入一般只对寄存器进行注入,无法精确模拟单粒子效应的实际注入情况,如注入组合逻辑模块等。

- 故障注入技术一般需要添加一段额外的处理器程序如故障注入控制程序,结果收集及分析模块等,因此需要确保额外的程序不会影响到原本处理器的正常工作且不会对故障注入结果造成干扰,这通常是难以精确控制的。

硬件层次故障注入技术

硬件层次的故障注入是在芯片流片后后进行是对实际的处理器芯片进行故障注入,通用的方法主要有引脚级注入法、重离子加速注入法、激光注入法以及电源电压注入法等,这是最接近于实际的故障环境。

优点

采用对实际芯片进行故障注入的方式来分析芯片的抗单粒子效应能力,可以在实际的处理器芯片中触发瞬态故障,翻转故障等,这是最贴近于实际情况的故障注入方式。

缺点

- 需要昂贵的硬件设备,如离子加速器造价昂贵,且资源紧张*

- 硬件层次的故障注入极有可能会对芯片造成损伤,代价高昂,增加了设计成本。

- 该层次的故障注入对象为实体芯片,必须等芯片流片后才能进行故障注入,增加了芯片的设计与制造周期。

- 难以将故障注入技术实现全自动化,因为芯片级的故障注入需要相当数量的故障次数才能使故障注入分析结果具有统计意义,这需要耗费大量的时间。

- 难以精确定位引起芯片运行错误的故障注入点。

RTL 层次故障注入技术

RTL 级故障注入技术是针对系统电路的行为级模型进行故障注入,其通常用硬件描述语言如 VHDL,verilog HDL 来实现。

优点

- 硬件描述语言具有对电路良好的建模与抽象功能,可以从不同的抽象级别来对处理器内部各个模块进行单粒子效应故障注入,如行为级故障注入仿真,逻辑门级故障注入仿真。

- 在 RTL级可以精确地对每个逻辑门或者接口信号进行数值仿真与分析,所以可以精确地控制故障注入的注入时间,注入位置等,更加有利于监控单粒子注入后处理器系统的故障行为。

- 在电路设计阶段就能进行故障注入与单粒子效应敏感性分析。根据分析结果就可以在设计阶段采取相应的加固措施来提高处理器的抗辐射能力,因此降低了抗辐射电路的设计成本与与设计周期,有效地加快了抗辐射芯片的研发速度。

缺点

verilog HDL 等硬件描述语言进行建模的电路属于数字电路,只有 0 与 1 两种工作状态,对应于模拟电路中的高低电平两种状态。使用 RTL 级故障注入技术忽略了单粒子效应的底层物理细节,只是单纯的改变电路的工作状态。而高能粒子入射期间后引发的瞬态脉冲电流有可能位于高低电平之间的中间区域,RTL 级故障注入技术无法精确地对这种类型的粒子入射进行模拟入射。

SPICE 层次网表故障注入技术

SPICE 级网表故障注入技术是针对电路的管级网表模型进行仿真的。从管级网表的特征来分析,因为管级网表体现了电路晶体管的物理特性和电学特性,涉及到具体电压值的改变,不是由简单的 0 或者 1 来表示,表示方式更加准确,因此在最底层晶体管级进行故障注入是最贴近于实际情况且最精确的故障注入技术。

前提

- 首先需要对目标处理器系统进行高精度的 SPICE 建模,进而建立正确的管级模型。*

- 需要建立准确的故障注入源,一般情况下,管级网表的故障注入源由器件级单粒子效应仿真结果得到的电流响应数据为基础,通过数学模型的拟合,可以得到不同 LET 值的瞬态脉冲电流源模型作为故障注入源。

优点

贴近底层晶体管,能够更加准确实际的描述单粒子效应故障入射的情况。

缺点

在仿真过程了添加了许多物理和电学特性,这导致了 SPICE 管级网表进行仿真的速度过慢,一般只支持小型集成电路。

SPICE 混合仿真

既考虑了器件级的仿真精度,又兼顾了电路级、RTL 级的仿真规模与速度,解决了现有方法的部分不足。

单粒子脉冲注入模型建模

需要通过器件级单粒子效应仿真来分析单粒子瞬态电流数据,得到单粒子效应在不同LET 条件下,产生的瞬态电流脉冲注入模型。

首先通过器件级离子注入仿真粒子入射MOSFET 器件电流数据,对数据进行处理,转换为符合SPICE 语法的PWL 电流源模型,最终得到不同能量粒子轰击半导体器件产生的单粒子瞬态电流脉冲注入模型

提取电路敏感节点

对待注入模块的 SPICE 网表进行处理,提取出该模块的敏感节点,得到敏感节点列表文件。

[!info]+ 电路敏感节点

NMOS 收集迁移率更高的电子,因此在相同入射条件,相同时间内,NMOS 总能收集更多的载流子从而产生更大的单粒子瞬态电流,体现出更强的单粒子瞬态效应。本文定义电路敏感节点为SPICE 网表中每个NMOS 晶体管的漏极。本文定义电路敏感节点为SPICE 网表中每个NMOS 晶体管的漏极。

敏感节点故障注入

得到待注入模块网表的敏感节点列表之后,就可以对该模块的敏感节点进行单粒子随机或定点故障注入。

该步骤用 Perl 脚本实现,自动生成故障注入文件。通过用户设定的单粒子 LET值,注入时间范围,注入时间步长(纳秒),注入模块名称等参数,脚本会结合待注入模块的敏感节点列表和单粒子脉冲注入模型,对脉冲电流源进行参数处理,得到包含单粒子注入信息的故障注入文件。

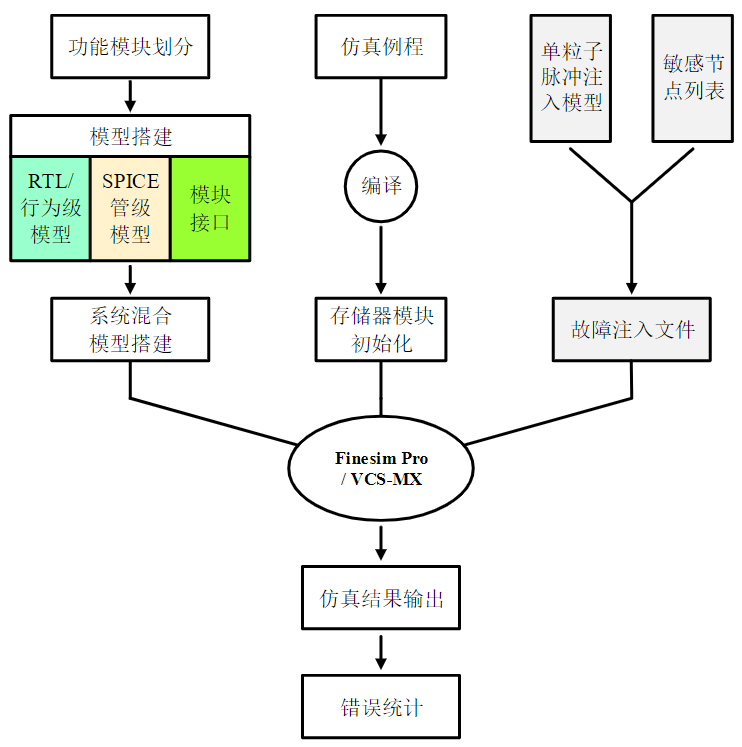

SPICE 混合仿真

获得单粒子瞬态脉冲电流源模型以及对待注入模块的敏感节点提取并生成故障注入文件之后,就可以使用 SPICE 仿真工具对目标系统进行单粒子效应仿真。

然而对于规模较大的星载计算机系统,直接使用 SPICE 仿真器进行电路级单粒子仿真,需要的仿真时间以及运算资源都会非常大。

因此本文(柳炜鑫论文)在电路级基础上进行改进,提出基于SPICE 混合仿真的单粒子效应仿真方法。

第一步,讨论单粒子注入方案,对目标系统进行模块划分。明确单粒子注入位置(如整数单元、总线控制器或者SRAM 等等),根据注入需求,将系统划分成各种功能模块。

第二步,分别搭建系统模块不同层级的模型。完成目标系统的模块划分后,为了减小仿真中SPICE 网表的规模,本文采用的方案是对待注入模块需要得到SPICE管级模型,而对于不需要进行单粒子故障注入的模块则可以建立其行为级模型或 RTL模型。

第三步,完成接口网络(Mixed Nets)的搭建。这个模块是用于在混合信号仿真中实现模拟和数字模块之间连接的信号网络,位于模拟模块和数字模块的边界。在混合仿真中,根据需要仿真器需要根据信号的传输方向,将混合信号进行 D2A 转换,以将数字逻辑值转换为模拟电压量,反之亦然。该接口网络为理想网络,D2A 转换中的默认高低电压值分别是SPICE 网表中的VDD 和0V。A2D 转换中默认的电压阈值为VDD 的50%。可以根据需要使用d2a 和a2d 命令对这些值进行修改。

第四步,完成系统的连接。将各模块所搭建的不同层级模型,通过接口网络实现整个目标系统的连接。

第五步,进行混合仿真。得到了目标系统的混合模型,就可以使用 VCS-MX 和Finesim Pro 进行仿真工作。

第六步,输出仿真结果。等待仿真结束后,依据仿真网表中节点电压测量语句,会将需要观测的节点电压值通过文本的形式进行输出,最终得到单粒子效应仿真的结果。

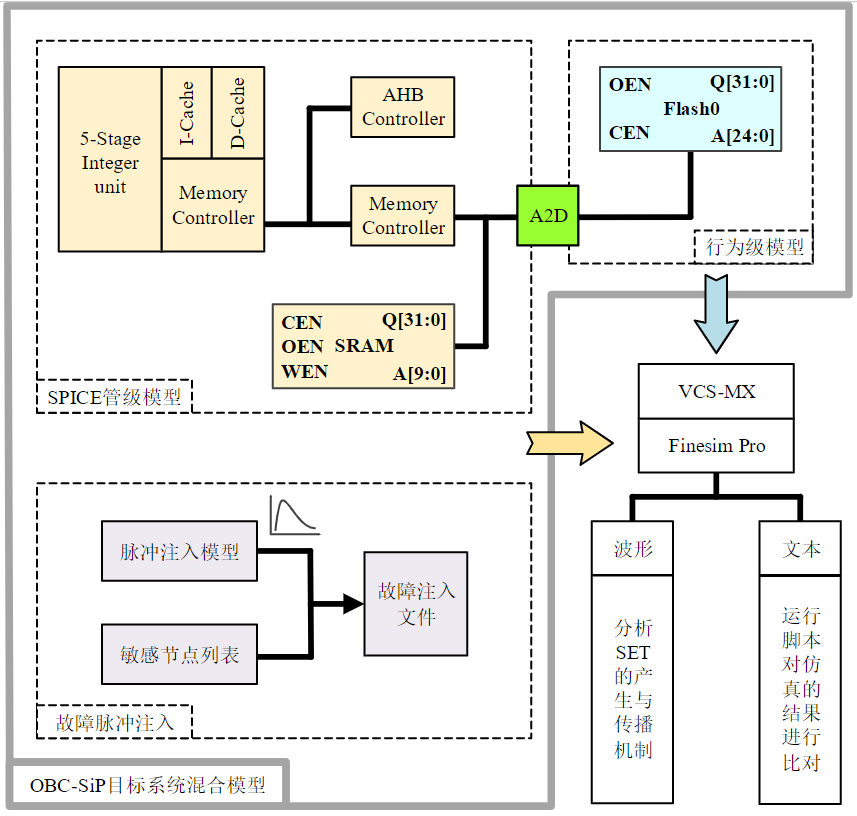

以OBC-SiP 目标系统模型进行单粒子效应仿真为例

首先完成模块划分,本例将处理器和 SRAM 作为待注入模块,因此系统中处理器和 SRAM 使用 SPICE 管级模型,而 Flash 模块使用行为级模型。

然后是完成接口网络搭建,对于使用VCS-MX和Finesim Pro进行VHDL / Verilog-SPICE 的流程中,该工具会自动插入A2D 和D2A 模块。

接下来使用接口网络完成系统的连接;完成系统混合模型之后,输入命令提交仿真。

等待仿真结束,就完成了一次对 OBC-SiP 目标系统的单粒子故障注入仿真,接下来就可以对仿真器输出的结果进行仿真比对以及系统错误统计。

柳师兄论文调研

荀师兄论文调研

通过 Perl 与 Shell 脚本实现了仿真中的数据测量、结果比对等工

作,并针对混合仿真提出了一种混合电路模块快速划分方法,有效地提升了仿真效率。

提出了 SiP 系统模块级单粒子效应敏感性的仿真方案;采用三阶矩阵乘法的程序指令,分别针对目标 SiP 系统中的整数处理单元、寄存器堆、缓存、AMBA 总线控制器、存储控制器、指令 SRAM 和数据 SRAM 进行仿真分析,发现数据 SRAM 具有 5.57%的系统软错误率,远高于系统其余模块,需要在系统抗单粒子效应加固设计时重点考虑。

基于 SiP 系统模块级单粒子效应敏感性的仿真方案,提出了面积等效的分析方法,进一步实现了全电路的混合仿真。

吕师兄论文调研

实现了一种基于断点分析的多点故障注入技术,该技术在传统的单点故障注入方法基础上进行改进而来,通过在单粒子效应系统级仿真过程中加入断点的方式,在上一级仿真结果的基础上加入下一级故障注入点,这样可以有效地多次注入故障注入点,同时保证了相邻故障注入点之间的结果非相干性。

通过在星载计算机系统中加载矩阵乘法程序并进行 SPICE 仿真,得到在运行该程序的基础上可以实现的最小故障注入间隔时间。