1. DUT——router功能概述

1.1管脚图

以router(路由器)为例

2. 实验代码

//********************************** stimulator **********************************//

module rt_stimulator(

input clock

,input reset_n

,output logic [15:0] din

,output logic [15:0] frame_n

,output logic [15:0] valid_n

,input [15:0] dout

,input [15:0] valido_n

,input [15:0] busy_n

,input [15:0] frameo_n

);

//for debug purpose from waveform //定义检测状态的变量

typedef enum {DRV_RESET,DRV_IDLE,DRV_ADDR,DRV_PAD,DRV_DATA} drv_state_t;

drv_state_t dbg_state;

byte unsigned dbg_din_chnl0_data;

initial begin : drive_reset_proc //reset阶段,复位时,reset_n为低电平,frame_n和valid_n为高电平

@(negedge reset_n);

dbg_state <= DRV_RESET;

din <= 0;

frame_n <= 1;

valid_n <= 1;

end

// drive chaannel 0 - chanel 15 (din[15:0])定义数据输出地址及数据

bit [3:0] addr;

byte unsigned data[];

initial begin : drive_chnl0_proc

@(negedge reset_n);

repeat(10) @(posedge clock);//延迟10个时钟周期

addr = 3; //从第3位输出

data = '{8'h33,8'h77};

// drive address phase 输入地址位阶段

for(int i=0;i<4;i++)begin //4 clock

@(posedge clock);

dbg_state <=DRV_ADDR;

din[0] <= addr[i];

valid_n[0] <= $urandom_range(0,1); //valid_n在din的地址输入时间段可为任意值x

frame_n[0] <= 1'b0; //frame_n需要为低

end

// drive pad phase //隔离阶段

for (int i=0;i<5;i++)begin //5 clock

@(posedge clock);

dbg_state <=DRV_PAD;

din[0] <= 1'b1;

valid_n[0] <= 1'b1; //valid_n需为高电平

frame_n[0] <= 1'b0; //frame_n需为低电平

end

// drive data phase 传输数据阶段

foreach(data[id])begin

for(int i=0;i<8;i++)begin

@(posedge clock);

dbg_state <=DRV_DATA;

dbg_din_chnl0_data <= data[id];

din[0] <= data[id][i];

valid_n[0] <=1'b0;

frame_n <= (id == data.size()-1 && i == 7) ? 1'b1 : 1'b0;//packet最后一位输出数据时frameo_n为高

end

end

// drive idle phase 闲置(没有数据传输)阶段

@(posedge clock);

dbg_state <=DRV_IDLE;

dbg_din_chnl0_data <= 0;

din[0] <= 1'b0;

valid_n[0] <= 1'b1;

frame_n <= 1'b1;

end

endmodule

//********************************** tb **********************************//

module lab3tb;

bit clk,rstn;

logic [15:0] din, frame_n, valid_n;

logic [15:0] dout, valido_n, busy_n, frameo_n;

// 产生时钟,周期为10ns

initial

forever #5ns clk <= !clk;

// 产生复位信号

initial begin

#2ns rstn <= 1;

#10ns rstn <= 0;

#10ns rstn <= 1;

end

//例化router为DUT

router dut(

.reset_n(rstn),

.clock(clk),

.* //其余端口名称均相同

);

//例化stimulator

rt_stimulator stim(

.reset_n(rstn),

.clock(clk),

.*

);

endmodule

3. 仿真结果

另,关于vim编辑器

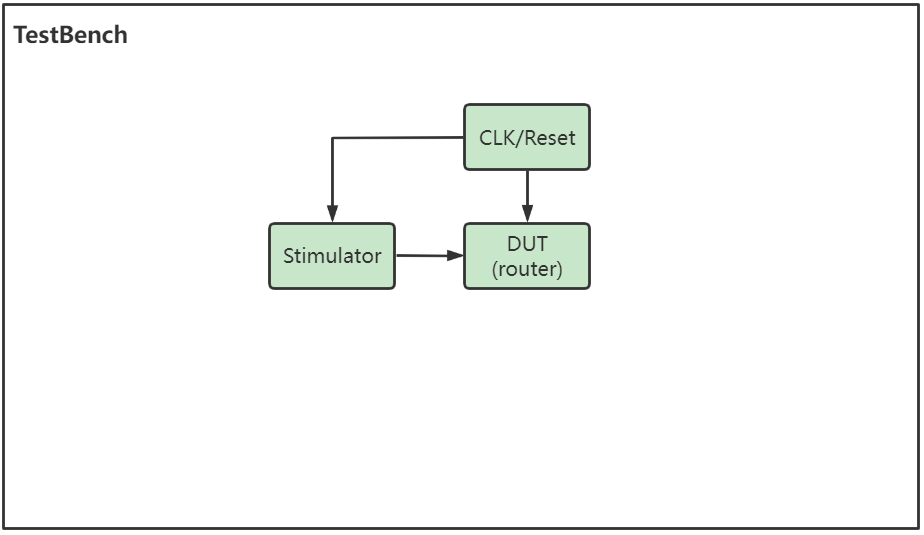

4. 初步TestBench平台概览